DESIGN

SEPTEMBER/OCTOBER 1982

Have the proponents of so-called "silicon compilers" seen the light?

Publisher Douglas G. Fairbairn

Editor-in-Chief Jerry Werner

Managing Editor Barbara S. Haymond

Technical Editor Barbara Clifford

Contributing Editor William D. Jansen

Technical Advisors Allen F. Podell Dr. Daniel G. Schweikert Dr. Carlo H. Séquin

Editorial/Circulation Monica Berg

**Director of Promotion** and Circulation Joy Deason Mole

Circulation Manager Lorri Ungaretti

Design Consultant Mike Shenon

Designer Chuck Walker

Artist Willy Keats

### Sales Representatives

West Coast Neal Manning (415) 966-8340 Charles Winnicky (201) 234-9497

VLSI DESIGN, September/October 1982, Volume III, No. 5. Publication of Redwood Systems Group, P.O. Box 50518, Palo Alto, CA 94303-0518. (415) 966-8340. Copyright 1982 Redwood Systems Group. All rights reserved. Reproduction in whole or in part without permission is prohibited. The subscription rates for VLSI DESIGN are \$19,95/6 issues and \$37.95/12 issues (U.S.); \$29.55/6 issues and \$57.15/12 issues (Canada); \$45/6 issues and \$90/12 issues (Europe/S.Am./Mexico/C.Am.); and \$55/6 issues and \$110/12 issues (Japan/Asia/Australia). Foreign rates include airmail delivery (except Canada). All payments must be made in U.S. dollars drawn on a U.S. bank. Foreign subscriptions must be prepaid.

VLSI DESIGN (USPS 565-870, ISSN vLS1 DESIGN (USPS 305-87), ISSN 0279-2834) is published six times a year by Redwood Systems Group, P.O. Box 50518, Palo Alto, CA 94303-0518. Second class controlled circulation postage paid at Mountain View, CA and additional entry office, San Jose, CA.

POSTMASTER: Send address changes to VLSI DESIGN, P.O. Box 50518, Palo Alto, CA 94303-0518

VLSI DESIGN was founded to explore, expand, and define the interrelations between very-large-scale integrated circuits (VLSI) and computer architecture, design strategies, costs, and aids, as well as the electronics industry as a whole. VLSI DESIGN is unique in that it is written by and for the participants in this dynamic field. VLSI DESIGN intends to be the communication focus of a new VLSI design community, encourage its development, and help define its directions.

Volume III, No. 5 September/October 1982

### Cover

Some people are calling the "silicon compiler" a breakthrough in the field of VLSI design. These advocates liken the present state of VLSI design tools to the early days of assembly-language computer programming, and believe the silicon compiler is the obvious next step. Its detractors contend that "silicon compiler" is a buzz-phraseand little else. Cover illustration by Mike Shenon, Palo Alto, California.

# Departments

- Calendar

- From the Editor

- News

- People

- Literature Review

- Designer's Corner Using a Silicon Compiler to **Generate IC Test Structures**

- **68** Product Showcase A Survey of IC CAD Tools for Design, Layout, and Testing

- 74 University Scene

- Advertisers' Index

Page 56

Page 27

Page 46

Page 62

## 16 Conference Preview: The 1982 International Test Conference

This annual event (still commonly referred to as the "Cherry Hill Test Conference") is "cherry" in another respect: It deals in large part with the problems and issues of VLSI testing.

#### 20 VLSI CAT: Filling the Void Between CAD and Testing

Robert Albrow, GenRad Semiconductor Test, Inc. Gordon Robinson, Cirrus Computers, Ltd.

The authors believe that computer-aided testing (CAT) for VLSI has been largely ignored. They explain why an integrated approach to computer-aided design (CAD) and CAT could reap significant rewards.

#### 27 Running RISCs

John K. Foderaro, Korbin S. Van Dyke, and David A. Patterson Computer Science Division, University of California at Berkeley

Last fall, the folks at U.C. Berkeley described the RISC processor, and predicted that it would be faster than both the Z8000 and the VAX. In this issue, they report their experience in implementing the RISC chip, and explain why some of their predictions panned out-and others didn't.

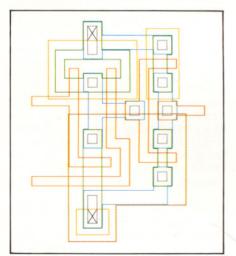

### The Silicon Compiler: Panacea, Wishful Thinking, or Old Hat?

Jerry Werner, Editor-in-Chief

Hardly an IC or CAD conference goes by, nowadays, without a paper (or even a full session) devoted to the "silicon compiler." This article defines the "ideal" silicon compiler, and explains the differences between approaches to so-called "silicon compilation.'

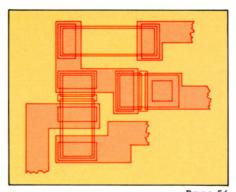

# 62 Portable Design Rules for Bulk CMOS

Thomas W. Griswold, Caltech Jet Propulsion Laboratory

VLSI designers have used portable, simplified design rules for nMOS ICs for about two years. However, CMOS does have specific performance advantages over nMOS. This article proposes a straightforward set of CMOS geometrical design rules that should be palatable to designers who are used to nMOS rules.