DCNW33394304 0409821003 LYNN CGNWAY 1182 XERGX CGRP VLD 3333 COYOTE HILL RD PALO ALTO CA 94304

DESIGN

NOVEMBER/DECEMBER 1982

Publisher Douglas G. Fairbairn

Editor-in-Chief Jerry Werner

Managing Editor Barbara S. Haymond

Technical Editor Barbara Clifford

Contributing Editor William D. Jansen

Technical Advisors Robert P. Larsen Allen F. Podell Dr. Daniel G. Schweikert Dr. Carlo H. Séquin

Editorial/Circulation Monica Berg

Director of Promotion and Circulation

Joy Deason Mole

Circulation Manager Lorri Ungaretti

Design Consultant Mike Shenon

Designer Willy Keats

Sales Representatives

West Coast East Coast Charles Winnicky (201) 234-9497 Neal Manning (415) 966-8340

VLSI DESIGN, November/December 1982, Volume III, No. 6. Publication of Redwood Systems Group, P.O. Box 50518, Palo Alto, CA 94303-0518. (415) 966-8340. Copyright 1982 Redwood Systems Group. All rights reserved. Reproduction in whole or in part without permission is prohibited. The subscription rates for VLSI DESIGN are \$19.95/6 issues and \$37.95/12 issues (U.S.); \$29.55/6 issues and \$57.15/12 issues (Canada); \$45/6 issues and \$90/12 issues (Europe/S.Am./Mexico/C.Am.); and \$55/6 issues and \$110/12 issues (Japan/Asia/Australia). Foreign rates (Japan/Asia/Australia). Foreign rates include airmail delivery (except Canada). All payments must be made in U.S. dollars drawn on a U.S. bank. Foreign subscriptions must be prepaid.

VLSI DESIGN (ISSN 0279-2834) is published six times a year by Redwood Systems Group, P.O. Box 50518, Palo Alto, CA 94303-0518. Second class controlled circulation postage paid at Mountain View, CA and additional entry office, San Jose, CA.

POSTMASTER: Send address changes to VLSI DESIGN, P.O. Box 50518, Palo Alto, CA 94303-0518.

VLSI DESIGN was founded to explore, expand, and define the interrelations between very-large-scale integrated circuits (VLSI) and computer architecture, design strategies, costs, and aids, as well as the electronics industry as a whole. VLSI DESIGN is unique in that it is written by and for the participants in this dynamic field. VLSI DESIGN intends to be the communication focus of a new VLSI design community, encourage its development, and help define its directions.

Volume III, No. 6 November/December 1982

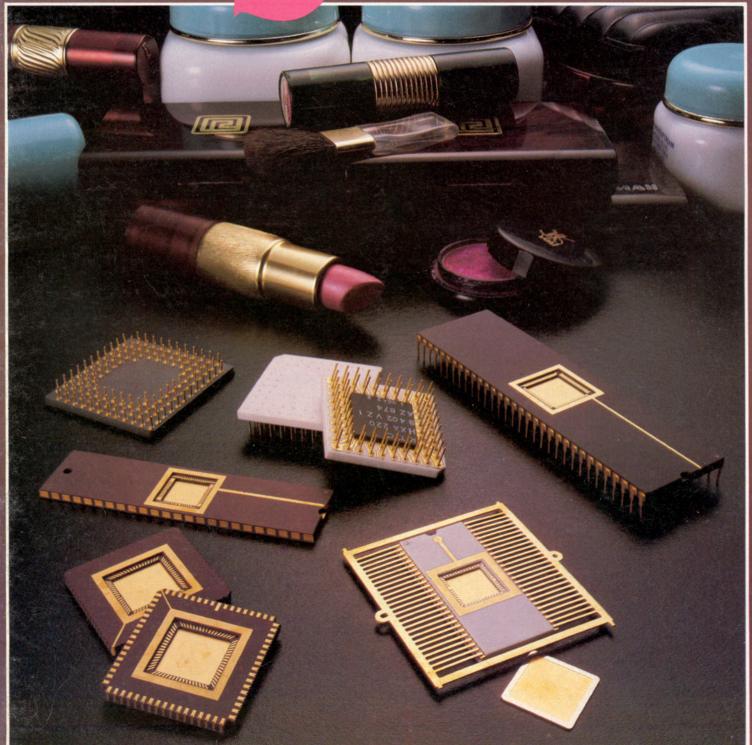

#### Cover

Although VLSI packages are often quite attractive, their selection is not merely a matter of cosmetics. VLSI designers must go beyond simple pin-count and package "footprint" considerations, and look into power dissipation, parasitics arising from dieto-package wiring, and the ease of mounting VLSI devices on printed-circuit boards. Cover photo by Jay Carlson, San Francisco, CA. LSI/VLSI packages provided by Signetics Corporation, Sunnyvale, CA.

# Departments

- Letters

- Calendar

- From the Editor

- News

- People

- **Product Showcase** Metheus λ750 VLSI Design System

- Technology Insight MOS Takes a Cue from the Bipolar World

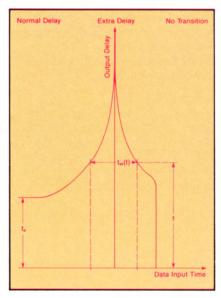

- 56 Designer's Corner How to Avoid **Synchronization Problems**

- **62** University Scene

- Advertisers' Index

Page 56

Page 16

Page 28

Page 44

## **Articles**

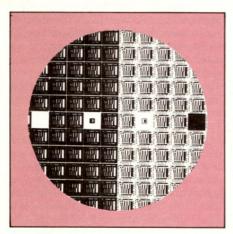

### 16 A High-Performance Configurable Microprocessor

David Bondurant, Michael Kopman, Michael Kalm, and Philip Bytheway, Honeywell, Inc., Solid State Electronics Division

The authors explain how and why they designed a single macro-cell-based chip that can be "configured" by metal-mask changes into several different high-performance microprocessors. Although this may sound like a standard gate-array approach, it's really quite different.

### VHSIC: The Focus Shifts from Microns to Systems

Jerry Werner, Editor-in-Chief

The Department of Defense's Very High Speed Integrated Circuit (VHSIC) program, originally regarded as a technology effort, is now more concerned with the systems aspects of VLSI.

#### 28 Five Pitfalls to Avoid When Obtaining Optical Photomasks

James N. Wiley and Duffy Zakaib, Master Images, Inc.

Although optical methods are by far the most common approach to making IC masks, IC designers who are unfamiliar with this business often make costly mistakes. This article explains how to avoid the most common snafus.

#### 36 Interfacing with E-Beam Mask Suppliers

Edward M. Morgan and Robert P. Smith, SandCastles

The authors explain the intricacies of doing business with electron-beam-mask suppliers. The article includes a table listing all U.S. merchant-market e-beam mask makers and their capabilities.

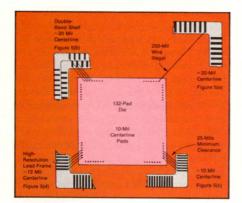

#### Practical Considerations in VLSI Packaging

S. Ralph Parris and John A. Nelson,

**Burroughs Corporation**

Dual-inline packages (DIPs) clearly are unsuitable for LSI/VLSI devices that require more than 64 pins; but no standard package has yet emerged for high-pin-count ICs. The authors describe the design/performance ramifications of the most popular VLSI packaging alternatives.