# DESIGN MAY/JUNE 1983 A CMP Publication

Some tools are optimized for the "tall, thin" designer.

Editor-in-Chief Jerry Werner

**Managing Editor** Barbara S. Haymond

**Editorial Consultant** Douglas G. Fairbairn

Technical Editor Barbara Clifford

Technical Advisors Robert P. Larsen Allen F. Podell Dr. Daniel G. Schweikert Dr. Carlo H. Séquin Constantin C. Timoc

Editorial/Circulation Monica Berg

Circulation Manager Lorri Ungaretti

Design Consultant Mike Shenon

Designer Yoshimi Stokes

Vice President/Group Publisher Richard Singer

Publisher John Sly

Associate Publisher Joy Deason Mole

Advertising Coordinator Anne Dodge

VLSI DESIGN, May/June 1983, Volume IV, No. 3. Publication of CMP Publications, Inc., P.O. Box 50518, Palo Alto, CA 94303-0518. (415) 966-8340. Copyright 1983 CMP Publications, Inc. All rights reserved. Reproduction in whole or in part without permission is prohibited. The subscription rates for VLSI DESIGN are \$29.95/12 issues and \$47.50/24 issues (U.S.); call VLSI Design at (415) 966-8340 for foreign subscription at (415) 966-8340 for foreign subscription rates. All payments must be made in U.S. dollars drawn on a U.S. bank. Foreign subscriptions must be prepaid.

VLSI DESIGN (ISSN 0279-2834) is published eight times in 1983 by CMP Publications, Inc., P.O. Box 50518, Palo Alto, CA 94303-0518. Second class controlled circulation postage paid at Mountain View, CA and additional entry office, San Jose, CA.

POSTMASTER: Send address changes to VLSI DESIGN, P.O. Box 50518, Palo Alto, CA 94303-0518.

VLSI DESIGN was founded to explore, expand, and define the interrelations between very-large-scale integrated circuits (VLSI) and computer architecture, design strategies, costs, and aids, as well as the electronics industry as a whole. VLSI DESIGN is unique in that it is written by and for the participants in this dynamic field. VLSI DESIGN intends to be the communication focus of a new VLSI design community, encourage its development, and help define its directions.

Over 27,900 copies of this issue printed.

CMP Publications, Inc. Gerard G. Leeds, President L. J. Leeds, Treasurer

Volume IV, No. 3 May/June 1983

### Cover

Just as mechanics' tools come in a variety of sizes for different mechanics and different applications, CAD tools for IC layout are also tailored to the user. Some CAD systems are meant for the "tall, thin designer"-one who handles the entire chip design from circuit simulation through IC layout. Other systems are designed for very specific (and very narrow) tasks. Cover photo by Victor Budnik, Palo Alto, CA. Snap-On® tools courtesy of Bob Atkinson, San Jose, CA.

# Departments

- Letters

- From the Editor

- Calendar

- People

- News

- **Product Showcase**

- Technology Insight A Perspective on Josephson Technology

- 78 Designer's Corner **Beyond Standard Cells**

- 84 **University Scene**

- VLSI DESIGN Billboard

- Classified Advertising

- Advertisers' Index

Page 78

# **Articles**

Page 30

Page 48

Page 64

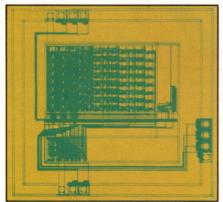

## An Example of Simplified Custom nMOS Design in Industry

Jeffrey C. Osborne and Michael A. Tremblay, Hewlett-Packard Company

The authors, who had no previous experience in IC design, found that several enhancements were required before a simplified design approach could be used in an industrial setting.

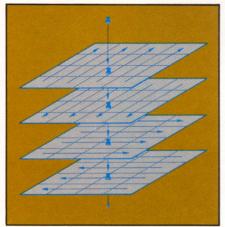

### The MacPitts Silicon Compiler: A View from the Telecommunications Industry

Jeffrey R. Fox, GTE Labs, Inc.

The author used the MacPitts software, developed at MIT Lincoln Laboratories, to implement several telecommunications chip layouts-including that of a Touch-Call® receiver IC that had been designed earlier using standard cells.

### 38 Conference Preview: The 1983 Design **Automation Conference**

The DAC is the foremost showcase for new developments in computer-aided design and design automation. This year's meeting includes an interesting twist: limited-attendance workshops, that will be held twice.

### 48 Recent Progress in CAD Systems for IC Layout

Jerry Werner, Editor-in-Chief

This round-up discusses current activities of the new companies who are (or soon will be) offering CAD tools for IC layout, and also reviews recent developments by traditional CAD suppliers.

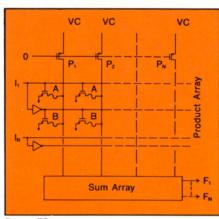

# AVLSI Legal Move Generator for the Game of Chess

Jonathan Schaeffer, Patrick A.D. Powell, Jim Jonkman Institute for Computer Research, University of Waterloo

The real trick in mapping a function onto a silicon chip lies in a careful statement of the problem, as this case study shows.