DCNW33394304 040982 803 LYNN CONWAY 0383 XEROX CORP VLD 3333 COYOTE HILL RD PALO ALTO CA 94304

DESIGN MARCH/APRIL 1983

It takes more than a visual once-over to reveal the real differences between CAE workstations.

Editor-in-Chief Jerry Werner

Managing Editor Barbara S. Haymond

Technical Editor Barbara Clifford

Technical Advisors Robert P. Larsen Allen F. Podell Dr. Daniel G. Schweikert Dr. Carlo H. Séquin

Editorial/Circulation Monica Berg

Circulation Manager Lorri Ungaretti

Design Consultant Mike Shenon

Designer Willy Keats

Publisher Douglas G. Fairbairn

Associate Publisher Joy Deason Mole

Advertising Coordinator Anne Dodge

## Sales Representatives

West Coast Neal Manning (408) 268-5649 East Coast Charles Winnicky (201) 234-9497

Midwest Norman Mole (815) 459-9004

VLSI DESIGN, March/April 1983, Volume IV, No. 2. Publication of Redwood Systems Group, P.O. Box 50518, Palo Alto, CA 94303-0518. (415) 966-8340. Copyright 1983 Redwood Systems Group. All rights reserved. Reproduction in whole or in part without permission is prohibited. The subscription rates for VLSI DESIGN are \$19.95/6 issues and \$37.95/12 issues (U.S.); \$29.55/6 issues and \$37.95/12 issues (Canada and Mexico); \$45/6 issues and \$90/12 issues (Europe/S.Am./C.Am.); and \$55/6 issues and \$110/12 issues (Japan/Asia/Australia). Foreign rates include airmail delivery (except Canada). All payments must be made in U.S. dollars drawn on a U.S. bank. Foreign subscriptions must be prepaid.

VLSI DESIGN (ISSN 0279-2834) is published six times a year by Redwood Systems Group, P.O. Box 50518, Palo Alto, CA 94303-0518. Second class controlled circulation postage paid at Mountain View, CA and additional entry office, San Jose, CA.

POSTMASTER: Send address changes to VLSI DESIGN, P.O. Box 50518, Palo Alto, CA 94303-0518.

VLSI DESIGN was founded to explore, expand, and define the interrelations between very-large-scale integrated circuits (VLSI) and computer architecture, design strategies, costs, and aids, as well as the electronics industry as a whole. VLSI DESIGN is unique in that it is written by and for the participants in this dynamic field. VLSI DESIGN intends to be the communication focus of a new VLSI design community, encourage its development, and help define its directions.

Over 25,500 copies of this issue printed.

Volume IV, No. 2 March/April 1983

### Cover

Several of the new breed of computer-aided engineering (CAE) workstations obviously *look* different from one another, but the real differences lie in the breadth of their respective applications software packages, and in their intended enhancements. These tools are to the VLSI designer what oscilloscopes and logic analyzers are to conventional circuit designers. Cover illustration by Nancy Freeman, San Francisco, CA.

# **Departments**

- 5 Letters

- 6 Calendar

- 8 From the Editor

- 10 People

- 17 News

- 43 Literature Review

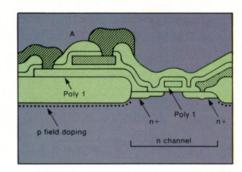

- 62 Technology Insight

Two-layer Metal CMOS vs.

Two-layer Poly CMOS

- 72 University Scene

- 78 VLSI DESIGN Billboard

- 80 Classified Advertising

- 80 Advertisers' Index

Page 62

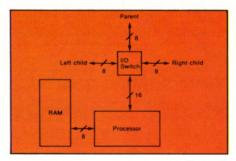

Page 72

# **Articles**

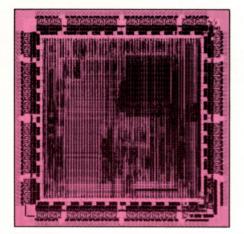

Page 34

Page 65

Page 58

## 18 The 1983 CICC

If you want to find out what the future holds for full-custom ICs and gate arrays, you needn't look beyond the fifth annual Custom Integrated Circuits Conference.

#### Software That Resides In Silicon 24

Ron Slamp and Jim Person, Intel Corporation

The authors point out several system-level issues that designers should consider before committing operating-system software to a chip.

### Testability and Maintainability with 34 a New 6K Gate Array

David R. Resnick, Control Data Corporation

This large gate array can test itself in the "Check-sum mode," using a pseudo-random number generator to create test operands.

## Sorting Out the CAE Workstations

Jerry Werner, Editor-in-Chief

This report describes the most useful features of the new computer-aided-engineering (CAE) workstations, and includes a comprehensive table of the various systems' capabilities.

## 58 Benchmarking the Workstations

Gary Robson, Array Technology, Inc.

The author describes the results of a benchmark test that all of the CAE workstation manufacturers were asked to run, and provides suggestions for readers who want to do their own benchmarking.

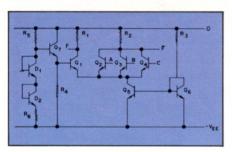

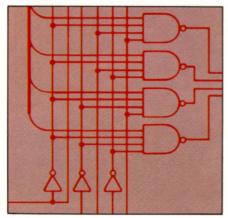

# 65 Stick-Layout Notation for Bipolar VLSI

M.I. Elmasry, University of Waterloo, Ontario, Canada

The author demonstrates how to use symbolic design notation to describe I2L, STTL, and ECL circuits.