Volume : 1A Chapter : 02 Section : Appendix

## IBM REGISTERED CONFIDENTIAL ACS-I Development Workbook

Page:

Date: 1/8/68

## ACS-1

## MPM INSTRUCTION MANUAL

| Part | <u>Title</u>                 |

|------|------------------------------|

| 1    | Load and Store Operations    |

| 2    | Move Operations              |

| 3    | Floating Point Arithmetic    |

| 4    | Integer Arithmetic           |

| 5    | Index Arithmetic             |

| 6    | Compare Operations           |

| 7    | Shift Operations             |

| 8    | Logical Operations           |

| 9    | Branch at Exit Operations    |

| 10   | Input/Output Operations      |

| 11   | Tag and Directory Operations |

| 12   | Special Registers            |

Volume

: 1A

Chapter

02

Section : Appendix

## IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1

Date: 1/8/68

## INDEX

| Mnemonic | <u>Name</u>                                     | <u>Page</u> |

|----------|-------------------------------------------------|-------------|

| ACH      | Add continued, high order                       |             |

| ACL      |                                                 | 4-9         |

| ADN      | Add continued, low order  Add double normalized | 4-8         |

| ADR      | Add double normalized  Add double rounded       | 3-10        |

| ADU      |                                                 | 3-11        |

| AI       | Add double unnormalized                         | 3-12        |

| AN       | Add integer                                     | 4-4         |

| ANDA     | Add normalized                                  | 3-10        |

|          | Logical and, arithmetic                         | 8-3         |

| ANDC     | Logical and, condition                          | 8-4         |

| ANDX     | Logical and, index                              | 8-3         |

| AR       | Add rounded                                     | 3-11        |

| AU       | Add unnormalized                                | 3-12        |

| AX       | Add index                                       | 5-4         |

| AXC      | Add index to short constant                     | 5-9         |

| AXCT     | Add index to short constant and test            | 5-14        |

| AXK      | Add index to constant                           | 5-9         |

| AXT      | Add index and test                              | 5-13        |

| BAND     | Branch if and                                   | 9-4         |

| BEQ      | Branch if equal                                 | 9-4         |

| BFAF     | Branch if false and false                       | 9-4         |

| BFOF     | Branch if false or false                        | 9-4         |

| BOR      | Branch if or                                    | 9-4         |

| BTAF     | Branch if true and false                        | 9-4         |

| BTOF     | Branch if true or false                         | 9-4         |

| BU       | Branch unconditionally                          | 9-4         |

| BXOR     | Branch if exclusive or                          | 9-4         |

Volume: 1A Chapter: 02

CVF

CVI

CVN

CVS

Chapter : 02 Section : Appendix

#### IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 2 Date: 1/8/68

3-28

4-11

4-11

3-27

CBA Compare bytes, arithmetic 6-10 CBMA Compare bytes multiple, arithmetic 6-10 CBMX Compare bytes multiple, index 6-11 CBX Compare bytes, index 6-11 CEQD Compare equal, double 6-4 CEQI Compare equal, integer 6-7 CEQN Compare equal, normalized 6-3 CEQX Compare equal, index 6-8 CEQXK Compare index with constant, equal 6-9 CGED Compare greater or equal, double 6-4 CGEI Compare greater or equal, integer 6-7 CGEN Compare greater or equal, normalized 6-3 CGEX Compare greater or equal, index 6-8 **CGEXK** Compare index with constant, greater or equal 6-9 CMEQD Compare magnitude equal, double 6-6 CMEQN Compare magnitude equal, normalized 6-5 **CMGED** Compare magnitude greater or equal, double 6-6 **CMGEN** Compare magnitude greater or equal, normalized 6-5 CNTAA Count leading alike, arithmetic 8-5 CNTAX Count leading alike, index 8-6 CNTDA Count leading different, arithmetic 8-5 CNTS Count to storage 1-7a CNTDX Count leading different, index 8-6 CNTT Count total ones, arithmetic 8-5 CUGEI Compare unsigned, greater or equal, integer 6-7 CUGEX Compare unsigned, greater or equal, index 6-8 CUGEXK Compare unsigned index with constant, greater or equal 6-9

Convert to full floating

Convert to normalized

Convert to short floating

Convert to integer

Volume

: 1A : 02

Chapter Section : Appendix

## IBM REGISTERED CONFIDENTIAL ACS-I Development Workbook Page: 3 Date: 1/8/68

| DDN   | Divide double normalized                         | 3-22 |

|-------|--------------------------------------------------|------|

| DDR   | Divide double rounded                            | 3-23 |

| DEN   | Directory enter                                  | 11-3 |

| DENP  | Directory enter per physical                     | 11-3 |

| DEX   | Directory examine                                | 11-4 |

| DEXP  | Directory examine per physical                   | 11-4 |

| DI    | Divide integer                                   | 4-7  |

| DM    | Directory move and invalidate                    | 11-4 |

| DMI   | Divide mixed integer                             | 4-7  |

| DMN   | Divide mixed normalized                          | 3-24 |

| DMR   | Divide mixed rounded                             | 3-24 |

| DN    | Divide normalized                                | 3-22 |

| DR    | Divide rounded                                   | 3-23 |

| DRUX  | Divide with remainder, unsigned index            | 3-23 |

| DRUXK | Divide with remainder unsigned index by constant | 5-11 |

| DRX   | Divide with remainder, index                     | 5-5  |

| DRXK  | Divide with remainder index by constant          | 5-10 |

| DSC   | Directory search per count                       | 11-6 |

| DSI   | Directory search for invalid                     | 11-5 |

| DSS   | Directory search for smaller                     | 11-5 |

| DSW   | Directory swap                                   | 11-3 |

| DUX   | Divide unsigned index                            | 5-8  |

| DUXK  | Divide unsigned index by constant                | 5-12 |

| DX    | Divide index                                     | 5-6  |

| DXK   | Divide index by constant                         | 5-11 |

| EQA   | Logical equivalence, arithmetic                  | 8-3  |

| EQC   | Logical equivalence, condition                   | 8-4  |

| EQX   | Logical equivalence, index                       | 8-3  |

| EXIT  | Exit                                             | 9-6  |

| EXITL | Exit and save location                           | 9-6  |

|       |                                                  |      |

Volume

: 1A

Chapter Section

: 02 : Appendix

## IBM REGISTERED CONFIDENTIAL ACS-I Development Workbook

Page: 4

Date: 1/8/68

| FAFA          | Logical false and false, arithmetic               | 8-3   |

|---------------|---------------------------------------------------|-------|

| FAFC          | Logical false and false, condition                | 8-4   |

| FAFX          | Logical false and false, index                    | 8-3   |

| FOFA          | Logical false or false, arithmetic                | 8-3   |

| FOFC.         | Logical false or false, condition                 | 8-4   |

| FOFX          | Logical false or false, index                     | 8-3   |

| HIO           | Halt I/O                                          | 10-3a |

| IC            | Interrupt call                                    | 9-15  |

| IFA           | Insert field, arithmetic                          | 7-10  |

| IFX           | Insert field, index                               | 7-10  |

| IFZA          | Insert field and zero, arithmetic                 | 7-10  |

| IFZX          | Insert field and zero, index                      | 7-10  |

| <b>I</b> R    | Interrupt return                                  | 9-16  |

| ITUM          | Invalidate tag and update MS                      | 11-2  |

| ITUMA         | Invalidate tag and update MS per alternate key    | 11-2  |

| IVIB          | Invalidate instruction buffers and branch         | 9-11  |

| LA            | Load arithmetic                                   | 1-8   |

| LAA           | Load arithmetic per alternate key                 | 1-9   |

| LAH           | Load arithmetic (half word format)                | 1-8   |

| LAT           | Load arithmetic, true indexing                    | 1-14  |

| LATH          | Load arithmetic, true indexing (half word format) | 1-14  |

| LD            | Load double arithmetic                            | 1-12  |

| LDH           | Load double arithmetic (half word format)         | 1-12  |

| $\mathtt{LL}$ | Load left half arithmetic                         | 1-16  |

| LMA           | Load multiple arithmetic                          | 1-22  |

| LMAA          | Load multiple arithmetic per alternate key        | 1-23a |

| LMX           | Load multiple index                               | 1-18  |

| LMXA          | Load multiple index per alternate key             | 1-19  |

Volume : 1A Chapter Section

: 02 : Appendix

# IBM REGISTERED CONFIDENTIAL ACS-I Development Workbook Page: 5 Date: 1/8/68

| LR   | Load right half arithmetic             | 1-16 |

|------|----------------------------------------|------|

| LX   | Load index                             | 1-4  |

| LXA  | Load index per alternate key           | 1-4  |

| LXH  | Load index (half word format)          | 1-4  |

| MAC  | Move arithmetic bit to condition bit   | 2-6  |

| MAX  | Move arithmetic to index               | 2-2  |

| MCX  | Move condition bit to index bit        | 2-6  |

| MDN  | Multiply double normalized             | 3-17 |

| MDR  | Multiply double rounded                | 3-18 |

| MDU  | Multiply double unnormalized           | 3-19 |

| MI   | Multiply integer                       | 4-5  |

| MKL  | Move constant to left half arithmetic  | 2-3  |

| MKR  | Move constant to right half arithmetic | 2-3  |

| MLX  | Move location to index                 | 2-4  |

| MMI  | Multiply mixed integer                 | 4-5  |

| MMN  | Multiply mixed normalized              | 3-20 |

| MMU  | Multiply mixed unnormalized            | 3-20 |

| MN   | Multiply normalized                    | 3-17 |

| MOT  | Move one to T register bit             | 10-5 |

| MR   | Multiply rounded                       | 3-18 |

| MSX  | Move special to index                  | 2-4  |

| MSXZ | Move special to index and zero         | 2-5  |

| MTX  | Move T register to index               | 10-4 |

| MU   | Multiply unnormalized                  | 3-19 |

| MX   | Multiply index                         | 5-4  |

| MXA. | Move index to arithmetic               | 2-2  |

| MXC  | Move index bit to condition bit        | 2-6  |

| MXK  | Multiply index by constant             | 5-10 |

| MXS  | Move index to special                  | 2-4  |

| MXSO | Move index to special by oring         | 2-5  |

Volume Chapter Section

: 1A

: 02

: Appendix

## IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 6 Date: 1/8/68

| TXM   | Move index to T register               | 10-4  |

|-------|----------------------------------------|-------|

| MZT   | Move zero to T register bit            | 10-5  |

| ORA   | Logical or, arithmetic                 | 8-3   |

| ORC   | Logical or, condition                  | 8-4   |

| ORX   | Logical or, index                      | 8-3   |

| PAUSE | Pause                                  | 9-12  |

| PI    | Pause with interrupt                   | 9-12  |

| RC    | Reset channel                          | 10-3b |

| RND   | Round                                  | 3-25  |

| RUX   | Remainder unsigned index               | 5-8   |

| RUXK  | Remainder unsigned index by constant   | 5-12  |

| RX    | Remainder index                        | 5-6   |

| RXK   | Remainder index by constant            | 5-11  |

| SCAN  | Scan                                   | 9-17  |

| SCH   | Subtract continued, high order         | 4-9   |

| SCL   | Subtract continued, low order          | 4-8   |

| SDN   | Subtract double normalized             | 3-13  |

| SDR   | Subtract double rounded                | 3-14  |

| SDU   | Subtract double unnormalized           | 3-15  |

| SHA   | Logical shift arithmetic               | 7-4   |

| SHAC  | Logical shift arithmetic by constant   | 7-4   |

| SHD   | Logical shift double                   | 7-6   |

| SHDC  | Logical shift double by constant       | 7-6   |

| SHDX  | Logical shift double index             | 7-6   |

| SHDXC | Logical shift double index by constant | 7-6   |

| SHX   | Logical shift index                    | 7-4   |

| SHXC  | Logical shift index by constant        | 7-4   |

|       |                                        |       |

Volume Chapter Section

: 1A : 02 : Appendix

# IBM REGISTERED CONFIDENTIAL ACS-I Development Workbook Page: 7 Date: 1/8/68

| CT.   |                                                    |        |

|-------|----------------------------------------------------|--------|

| SI    | Subtract integer                                   | 4-4    |

| SIA   | Integer shift arithmetic                           | 7-12   |

| SIAC  | Integer shift arithmetic by constant               | 7-13   |

| SID   | Integer shift double                               | 7-15   |

| SIDC  | Integer shift double by constant                   | 7-15   |

| SIO   | Start I/O                                          | 10-2   |

| SIOA  | Start I/O per alternate key                        | 10-3a  |

| SIX   | Integer shift index                                | 7-12   |

| SIXC  | Integer shift index by constant                    | 7-13   |

| SKAND | Skip if and                                        | 9-9    |

| SKEQ  | Skip if equal                                      | 9-9    |

| SKFAF | Skip if false and false                            | 9-9    |

| SKFOF | Skip if false or false                             | 9-9    |

| SKOR  | Skip if or                                         | 9-9    |

| SKTAF | Skip if true and false                             | 9-9    |

| SKTOF | Skip if true or false                              | 9-9    |

| SKXOR | Skip if exclusive or                               | 9-9    |

| SN    | Subtract normalized                                | 3-13   |

| SNF   | Set negative, floating                             | 3-26   |

| SNI   | Set negative, integer                              | 4-10   |

| SNX   | Set negative, index                                | 5-13   |

| SPF   | Set positive, floating                             | 3-26   |

| SPI   | Set positive, integer                              | 4-10   |

| SPX   | Set positive, index                                | 5-13   |

| SR    | Subtract rounded                                   | 3-14   |

| STA   | Store arithmetic                                   | 1-10   |

| STAA  | Store arithmetic per alternate key                 | · 1-11 |

| STAH  | Store arithmetic (half word format)                | 1-10   |

| STAT  | Store arithmetic, true indexing                    | 1-14   |

| STATH | Store arithmetic, true indexing (half word format) | 1-14   |

| STD   | Store double arithmetic                            | 1-13   |

| STDH  | Store double arithmetic (half word format)         | 1-13   |

|       |                                                    |        |

Volume : 1A Chapter

: 02 : Appendix Section

## IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 8 Date: 1/8/68

| STL   | Store left half arithmetic                  | 1-16          |

|-------|---------------------------------------------|---------------|

| STMA  | Store multiple arithmetic                   | 1-23b         |

| STMAA | Store multiple arithmetic per alternate key | 1-23c         |

| STMX  | Store multiple index                        | 1-20          |

| STMXA | Store multiple index per alternate key      | 1-21          |

| STMZ  | Store multiple zeros                        | 1-24          |

| STMZA | Store multiple zeros per alternate key      | 1-24          |

| STR   | Store right half arithmetic                 | 1-16          |

| STX   | Store index                                 | 1-5           |

| STXA  | Store index per alternate key               | 1-6           |

| STXH  | Store index (half word format)              | 1-5           |

| SU    | Subtract unnormalized                       | 3-15          |

| SVC   | Supervisor call                             | 9-13          |

| SVR   | Supervisor return                           | 9-14          |

| sws   | Swap with storage                           | 1-7b          |

| SWSA  | Swap with storage per alternate             | 1-7b          |

| SX    | Subtract index                              | 5-4           |

| TAFA  | Logical true and false, arithmetic          | 8-3           |

| TAFC  | Logical true and false, condition           | 8-4           |

| TAFX  | Logical true and false, index               | 8-3           |

| TC    | Test channel                                | <b>10-3</b> b |

| TOFA  | Logical true or false, arithmetic           | 8-3           |

| TOFC  | Logical true or false, condition            | 8-4           |

| TOFX  | Logical true or false, index                | 8-3           |

| XORA  | Logical exclusive or, arithmetic            | 8-3           |

| XORC  | Logical exclusive or, condition             | 8-4           |

| XORX  | Logical exclusive or, index                 | 8-3           |

|       |                                             | = *           |

Volume Chapter 1A 02

Section

Appendix

#### IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-1 Date: 1/8/68

## LOAD AND STORE OPERATIONS

The load operations replace the contents of index (X) registers, or arithmetic (A) registers, with information from storage. The storage contents remain unchanged. The store operations replace information in storage with information from one or more of the X or A registers. The register contents remain unchanged. The count to storage and swap with storage instructions act as both a load and a store and thus may change both the register and storage.

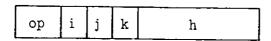

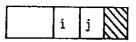

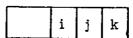

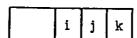

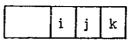

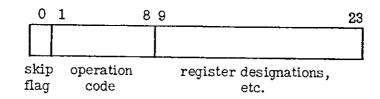

The load and store instructions have one of the following formats:

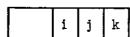

| Short | op | i | j | k |    |

|-------|----|---|---|---|----|

| Long  | op | i | j | k | h  |

|       | 9  | 5 | 5 | 5 | 24 |

For each operation the i field designates the register, or registers, to be loaded or stored. The j and k fields designate two index registers which are added together to calculate the effective address of the storage information. In the long format the h field is also added in forming the effective address.

All addresses generated by the main processor are considered to be virtual addresses by the mapping mechanism. This mechanism transforms (maps) the virtual address into the address of a physical location in storage. The mapping mechanism deals with 36 bit virtual addresses (ea). The low order 24 bits are called the effective address (eal) and the high order 12 bits are called the key (eak).

The eak is specified by one of four key registers: problem normal key PNK, problem alternate key PAK, supervisory normal key SNK, and supervisory alternate key SAK. Which key is used is defined by the MPM mode, which is either problem or supervisory, and the instruction code, which specifies either normal or alternate. The following table describes the key specification:

|               | Supervisory Mode | Problem Mode |

|---------------|------------------|--------------|

| Normal Key    | SNK              | PNK          |

| Alternate Key | SAK              | PAK          |

The eal may be computed in two ways. In normal indexing the index quantities are aligned so that the low order bits of each are added together. In true indexing the quantity from  $X^k$  is doubled by shifting it left one position prior to addition. The eal addition is computed modulo  $2^{24}$  for both types of indexing.

Volume Chapter : 1A

Section

: 02 : Appendix IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-2

Page: 1-2 Date: 1/8/68

The following table describes normal and true indexing for both long and short formats:

|                 | Short Format                         | Long Format                               |

|-----------------|--------------------------------------|-------------------------------------------|

| Normal Indexing | eal ≁X <sup>j</sup> + X <sup>k</sup> | eal + X <sup>j</sup> + X <sup>k</sup> + h |

| True Indexing   | eal + $X^j$ + 2 × $X^k$              | eal $+X^{j} + 2 \times X^{k} + h$         |

additions are computed modulo 224

X<sup>j</sup>, X<sup>k</sup> = contents of the index registers specified by the j and k fields of the instruction

h = literal field of the instruction

Index load and store operands are 24 bits long. The length of the operands for arithmetic loads and stores is specified in the operation code. Three lengths may be specified: half (24 bits), single (48 bits), and double (96 bits). When loading half word quantities the 24 bit number is expanded to 48 bits when placed in the arithmetic register as follows: if the instruction calls for the left half to be loaded, 0's replace the low order 24 bits of the register; if the right half is loaded, the high order bit of the half word is copied into the high order 24 bits of the register. When storing half word quantities, the selected half of the arithmetic register is stored and the register contents are uneffected.

Index register  $X^0$  is specified to be a source of 0's. To specify single indexing or no indexing, either the j or k field or both should be set to zero. When  $X^0$  is stored, 0's replace the 24-bit storage contents located by the effective address. Information loaded into  $X^0$  is not recoverable from  $X^0$ .

Similarly,  $A^0$  is specified to contain 0's. If  $A^0$  is used as a source in a store operation, the length of the zero quantity stored is determined by the operand length specified in the instruction. Information loaded into  $A^0$  is not recoverable from  $A^0$ . If  $A^0$  is specified by the i field of a load arithmetic double instruction, register  $A^1$  is also set to 0's.

Volume

: 1A

Chapter Section : 02 Appendix

#### IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-3a Date: 1/8/68

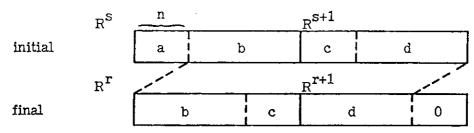

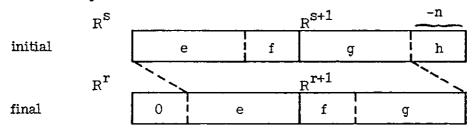

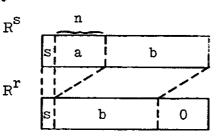

#### Multiple Load and Store

The multiple load operations replace the contents of blocks of successive arithmetic (A) or index (X) registers with information taken from consecutive storage locations. (Register number 0 is considered to be the successor of register number 31.) Storage remains unchanged.

The multiple store operations reverse the process, that is, information from the registers is stored in consecutive storage locations. The registers are unchanged.

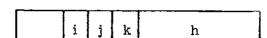

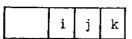

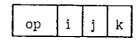

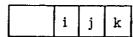

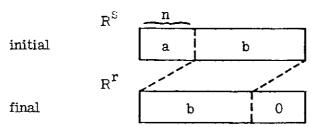

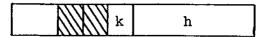

The multiple load and store operations have the following format:

For each operation the i-field designates the initial register to be loaded or stored; j gives the number of registers to be loaded or stored; and the modulo  $2^{24}$  sum of index register k and the literal, h, gives the effective address of the first storage location.

Registers  $\mathbf{X}^0$  and  $\mathbf{A}^0$  are sources of 0's; information loaded into them is not recoverable.

The value of the i-field must be even when X-unit operands are specified. If it is not, the low order bit of the field is forced to 0, exception bit RS is set, and the operation proceeds. The use of the register pair  $X^{0}$ , in multiple load and store instructions results in the loading or storing 24 0's for  $X^{0}$  and the 24 data bits for  $X^{1}$ .

#### Exceptions

Every virtual address generated for a load or store arithmetic, a load or store arithmetic double, or any multiple load or store, must be divisible by 2. If it is not, the BV (boundary value) exception bit is set to 1, and the operation proceeds using the address minus one as the storage address. Similarly the virtual address for STMZ and STMZA must be divisible by 64. If it is not, the BV bit is set to 1, and the operation proceeds using the address with the seven low order bits forced to 0's as the storage address.

The mapping mechanism checks the validity of all virtual addresses in two ways. First, if the virtual address does not correspond to an actual physical location, a missing address exception occurs and exception bit MA is set to 1. Second, if the virtual address of a store instruction refers to an area to which store access is not permitted, a protected address exception occurs and exception bit PA is set to 1. The setting of the MA or PA exception bit results in a type 2 interruption condition. See the chapter "Interruptions" for further details.

Each storage address generated for multiple load and store operations is individually checked for MA and PA exceptions.

Volume

1A

Chapter

: 02

Section : Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-3b Date: 1/8/68

When a double precision A-unit operand is specified by the instruction code, the value of the i-field is assumed to be even. If it is not, the low order bit of the i-field is forced to 0, exception bit RS is set, and the operation proceeds. These fifteen A-unit double precision quantities are specifiable; namely the data in register pairs specified by 2, 4, 6,  $\dots$ , 30. The double precision quantity specified by  $A^0$  is defined to be 96 0's, so that register  $A^1$  is not the low order half of any double precision quantity.

Volume Chapter : 1A

Section

02 Appendix

## IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-4 Date: 4/17/67

| Load | Index | (half | word | format; | Ì |

|------|-------|-------|------|---------|---|

|      |       |       |      |         |   |

LXH

| i    | i | k |

|------|---|---|

| <br> |   |   |

eal

$$+X^{j} + X^{k}$$

eak +normal key

$$x^i + M^{ea}$$

Exceptions

Exception bit

missing address

MA

Load Index

LX

| i | l i | k | 'n |

|---|-----|---|----|

|   | 4   |   |    |

eal

$$+X^{j} + X^{k} + h$$

eak +normal key

$$x^{i} + M^{ea}$$

Exceptions

Exception bit

missing address

MA

Load Index per Alternate Key

LXA

$$eal + X^j + X^k + h$$

eak+ alternate key

This instruction is identical to LX except that in forming the storage address the alternate key is used.

Exceptions

Exception bit

missing address

MA

Volume

: 1A

Chapter

: 02

Section

: Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-5 Date: 4/17/67

Store Index (half word format)

STXH

i j k

eal

$$+ X^{j} + X^{k}$$

eak + normal key

$$M^{ea} + x^{i}$$

Exceptions

Exception bit

missing address

MA.

protected address

PΑ

Store Index

STX

i j k h

eal

$$+X^j + X^k + h$$

eak +normal key

$$M^{ea} + x^{i}$$

Exceptions

Exception bit

missing address

MA

protected address

PA

Volume

: 1A

Chapter

02

Section : Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-6

Date: 4/17/67

## Store Index per Alternate Key

STXA

| <br> |   |   |   |

|------|---|---|---|

| i    | j | k | h |

eal

$$+X^{j} + X^{k} + h$$

eak + alternate key

$$M^{ea} + x^{i}$$

This instruction is identical to STX except that in forming the storage address the alternate key is used.

Exceptions

Exception bit

missing address

MA

protected address

PΑ

Volume

: 1A

Chapter

: 02

Section

: Appendix

## IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-7a Date: 1/8/68

#### Count to Storage

| CNTS               |   | i | j | k | h |

|--------------------|---|---|---|---|---|

| eal $+X^j + X^k +$ | h |   |   |   |   |

$$X^{i} + M^{ea}$$

eak +normal key

If

$$M^{ea} \neq 2^{24}$$

-1:  $M^{ea} \leftarrow M^{ea} + 1$

If

$$M^{ea} = 2^{24} - 1$$

:  $M^{ea} + M^{ea}$

The contents of the memory location is loaded into  $X^i$ . The contents of  $M^{ea}$  is treated as an unsigned integer and is incremented by one, modulo  $2^{24}$ . If this would cause  $M^{ea}$  to go to zero, the add is suppressed. The fetch from ea and the subsequent storing into it are interlocked so that no intervening accesses are permitted.

Exceptions

Exception bit

missing address

MA

protected address

PA

Volume Chapter : 1A

Section

02 Appendix

## IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-7b

Date: 1/8/68

## Swap with Storage

sws i

i j k h

$eal + X^{j} + X^{k} + h$

eak + normal key

If  $M^{ea} \neq 0$ :  $X^{i} + M^{ea}$

If  $M^{ea} = 0$ :  $X^{i} + M^{ea}$  and  $M^{ea} + X^{i}$

The contents of the memory location is loaded into  $X^i$ . If the contents of  $M^{ea}$  is zero (twenty-four 0's),  $M^{ea}$  is replaced by the original contents of  $X^i$ . If  $M^{ea}$  is different from zero,  $M^{ea}$  is not changed. The fetch from  $M^{ea}$  and the (potential)subsequent storing into it are interlocked so that no intervening accesses are permitted.

## Exceptions

Exception bit

missing address

protected address

MΑ

$\mathbf{p}_{\mathbf{A}}$

## Swap with Storage per Alternate Key

SWSA

$$eal + X^j + X^k + h$$

eak + alternate key

If  $M^{ea} \neq 0$ :  $X^i + M^{ea}$

If

$$M^{ea} = 0$$

:  $X^i + M^{ea}$  and  $M^{ea} + X^i$

This instruction is identical to SWS except that the alternate key is used.

Exceptions

Exception bit

missing address

MA

protected address

PΑ

Volume

Chapter

Section

: 1A : 02 : Appendix

IBM REGISTERED CONFIDENTIAL ACS-I Development Workbook

Page: 1-8 Date: 4/17/67

LAH

| <br> |     |   |

|------|-----|---|

| i    | j   | k |

|      | - 1 |   |

eal

$$+ X^{j} + X^{k}$$

eak + normal key

$$A^{i} + M^{ea}$$

Exceptions

Exception bit

missing address

ea not divisible by 2

MA

ΒV

## Load Arithmetic

LA

eal

$$+X^{j} + X^{k} + h$$

eak +normal key

Exceptions

Exception bit

missing address

MA

ea not divisible by 2

Volume

: 1A

Chapter

Section

: 02 : Appendix

IBM REGISTERED CONFIDENTIAL ACS-I Development Workbook

Page: 1-9 Date: 4/17/67

Load Arithmetic per Alternate Key

LAA

| <br>  |   |   |   |

|-------|---|---|---|

| <br>i | j | k | h |

$$eal + x^j + x^k + h$$

eak + alternate key

$$A^{i} \leftarrow M^{ea}$$

This instruction is identical to LA except that in forming the storage address the alternate key is used.

Exceptions

Exception bit

missing address

MA

ea not divisible by 2

Volume Chapter : 1A

Section

: 02

: Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-10 Date: 4/17/67

Store Arithmetic (half word format)

STAH

i k

eal

$$+ x^j + x^k$$

eak + normal key

Exceptions

Exception bit

missing address

protected address

ea not divisible by 2

MA

PA

BV

## Store Arithmetic

STA

i | j | k h

eal

$$+X^{j} + X^{k} + h$$

eak +normal key

M<sup>ea</sup> ←A<sup>i</sup>

Exceptions

Exception bit

missing address

MA

protected address

PΑ

ea not divisible by 2

Volume

: 1A

Chapter

: 02

Section : Appendix IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-11 Date: 4/17/67

## Store Arithmetic per Alternate Key

STAA

j k h

eal +

$$X^j + X^k + h$$

eak + alternate key

$$M^{ea} + A^{i}$$

This instruction is identical to STA except that in forming the storage address the alternate key is used.

| Exceptions            | Exception bit |

|-----------------------|---------------|

| missing address       | MA            |

| protected address     | PA            |

| ea not divisible by 2 | BV            |

Volume

: 1A

Chapter

: 02

Section

: Appendix

## IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-12 Date: 1/8/68

## Load Arithmetic Double (half word format) LDH

| <br> |   |   |

|------|---|---|

|      |   |   |

| l i  | i | k |

| _    |   |   |

$$eal + X^{j} + X^{k}$$

eak + normal key

$A^{i,i+1} + M^{ea,ea+2}$

Exceptions

Exception bit

missing address ea not divisible by 2

MA BV

. . .

5.5

i odd

RS

## Load Arithmetic Double

LD

i j k h

eal

$$+X^{j} + X^{k} + h$$

eak +normal key

$A^{i,i+1}$  +  $M^{ea,ea+2}$

Exceptions

i odd

Exception bit

missing address ea not divisible by 2 MA

BV RS

Volume Chapter : 1A

Section

: 02

: Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-13 Date: 1/8/68

| <u>Store Ar</u> | rithm | etic | Double |

|-----------------|-------|------|--------|

| (half           | word  | form | nat)   |

STDH

| <br> |   |   |

|------|---|---|

|      | _ |   |

| i    | j | k |

eal

$$+x^j + x^k$$

eak +normal key

$$M^{ea, ea+2} + A^{i, i+1}$$

| Exceptions            | Exception bit |

|-----------------------|---------------|

| missing address       | MA            |

| protected address     | PA            |

| ea not divisible by 2 | BV            |

| i odd                 | RS            |

## Store Arithmetic Double

STD

| <br> |    |     |   |

|------|----|-----|---|

| - 1  | ı  | 1   |   |

| li   | li | l k | h |

|      |    |     |   |

eal +

$$X^j + X^k + h$$

eak + normal key

$M^{ea, ea+2} \leftarrow A^{i, i+1}$

| Exceptions            | Exception bit |

|-----------------------|---------------|

| missing address       | MA            |

| protected address     | PA            |

| ea not divisible by 2 | BV            |

| i odd                 | RS            |

Volume Chapter : 1A 02

Section

: Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-14 Date: 4/17/67

## Load Arithmetic, True Indexing

(half word format)

LATH

| <br> |   |   |

|------|---|---|

| i    | j | k |

eal

$$+ x^{j} + 2 \times x^{k}$$

eak + normal key

$$A^{i} + M^{ea}$$

Exceptions

missing address ea not divisible by 2 Exception bit

MA

BV

## Load Arithmetic, True Indexing

LAT

|       |   |   | ·" |

|-------|---|---|----|

| l i l | 1 | k | h  |

|       |   |   |    |

eal

$$+X^{j} + 2 \times X^{k} + h$$

eak +normal key

$$A^{i} + M^{ea}$$

Exceptions

Exception bit

missing address ea not divisible by 2 MA

ΒV

Volume Chapter

: 1A 02

Section

: Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-15 Date: 4/17/67

Store Arithmetic, True Indexing

(half word format)

STATH

| i | j | k |

|---|---|---|

eal

$$+ X^j + 2 \times X^k$$

eak + normal key

$$M^{ea} + A^{i}$$

Exceptions

Exception bit

missing address protected address

MA PA

ea not divisible by 2

BV

Store Arithmetic, True Indexing

STAT

k h

eal

$$+X^{j} + 2 \times X^{k} + h$$

eak +normal key

mea +Ai

Exceptions

Exception bit

missing address protected address ea not divisible by 2 MA PA

Volume Chapter 1A

Section

02 Appendix IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-16 Date: 4/17/67

#### Load Arithmetic, Left Half

LL

| i | j | k | h |

|---|---|---|---|

$$eal + X^j + X^k + h$$

eak + normal key

$$A_{0,1,2,\cdots,23}^{i} + M^{ea}$$

Exceptions

missing address

Exception bit

MA

## Load Arithmetic, Right Half

LR

| <br> |       |   |       |

|------|-------|---|-------|

|      |       |   |       |

| l i  | l i i | k | l h l |

|      | J     |   | · · · |

eal

$$+X^{j} + X^{k} + h$$

eak +normal key

$$A_{0,1,\dots,23}^{i} + M_{0}^{ea}$$

[24]

$$A^{i}_{24,25,\dots,47} + M^{ea}$$

Exceptions

Exception bit

missing address

MA

Volume

1A

Chapter

02

Section : Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-17 Date: 4/17/67

#### Store Arithmetic, Left Half

STL

i j k h

$$eal + X^j + X^k + h$$

eak + normal key

$$M^{ea} \leftarrow A^{i}_{0,1,2,\cdots,23}$$

Exceptions

Exception bit

missing address

protected address

MA

PA

## Store Arithmetic, Right Half

STR

| i | j | k | h |

|---|---|---|---|

$$eal + X^{j} + X^{k} + h$$

eak + normal key

$$M^{ea} + A^{i}_{24,25,26,\cdots,47}$$

Exceptions

Exception bit

missing address

protected address

MA

PA

Volume Chapter 1A

Section

: Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-18 Date: 1/8/68

#### Load Multiple Index

LMX

i j k h

number of registers loaded + j

eal

$$+ X^k + h$$

eak + normal key

$$x^{i,i+1} + M^{ea,ea+1}$$

$$x^{i+2, i+3} + M^{ea+2, ea+3}$$

• • • • •

$$X^{i+j-2, i+j-1} + M^{ea+j-2, ea+j-1}$$

If j is not divisible by 2, the number of registers loaded will be j-1. If j is zero or one, 32 registers will be loaded.

| Exceptions            | Exceptions |

|-----------------------|------------|

| missing address       | MA         |

| ea not divisible by 2 | BV         |

| i odd                 | RS         |

Volume

: 1A

Chapter Section

02

: Appendix

#### IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-19 Date: 1/8/68

## Load Multiple Index per Alternate Key

LMXA

j k h

number of registers loaded + j

eal

$$+ X^k + h$$

eak + alternate key

$$X^{i,i+1} + M^{ea,ea+1}$$

$$x^{i+2, i+3} + M^{ea+2, ea+3}$$

$X^{i+j-2, i+j-1} + M^{ea+j-2, ea+j-1}$

If j is not divisible by 2, the number of registers loaded will be j-1. If j is zero or one, 32 registers will be loaded.

| Exceptions |

|------------|

| TWOCDMOND  |

Exception bit

missing address

ea not divisible by 2

i odd

MA

BV

RS

Volume

: 1A

Chapter Section

02

: Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-20

Date: 1/8/68

## Store Multiple Index

STMX

j k h

number of registers stored + j

eal

$$+X^k + h$$

eak + normal key

$$M^{ea, ea+1} + X^{i, i+1}$$

$$M^{ea+2, ea+3} + X^{i+2, i+3}$$

$M^{ea+j-2}$ , ea+j-1 +  $X^{i+j-2}$ , i+j-1

If j is not divisible by 2, the number of registers stored will be j-1. If j is zero or one, 32 registers will be stored.

| Exceptions            | Exception bit |

|-----------------------|---------------|

| missing address       | MA            |

| protected address     | PA            |

| ea not divisible by 2 | BV            |

| i odd                 | RS            |

Volume Chapter : 1A : 02

Section

Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-21 Date: 1/8/68

## Store Multiple Index per Alternate Key

STMXA

i j k h

number of registers stored + j

$$eal + X^k + h$$

eak + alternate key

$$M^{ea, ea+1} \leftarrow X^{i, i+1}$$

$$M^{ea+2, ea+3} + x^{i+2, i+3}$$

$$M^{ea+j-2, ea+j-1} + x^{i+j-2, i+j-1}$$

If j is not divisible by 2, the number of registers stored will be j-1. If j is zero or one, 32 registers will be stored.

| Exceptions            | Exception bit |

|-----------------------|---------------|

| missing address       | MA            |

| protected address     | PA            |

| ea not divisible by 2 | BV            |

| i odd                 | RS            |

Volume Chapter 1A

Section

: Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-22 Date: 1/8/68

#### Load Multiple Arithmetic

LMA

i j k h

number of registers loaded + j

$$eal + X^k + h$$

eak + normal key

$$A^{i} + M^{ea}$$

$$A^{i+1} + M^{ea+2}$$

• • •

$A^{i+j-1} \leftarrow M^{ea+2j-2}$

If j is zero, 32 registers will be loaded.

Exceptions

missing address

ea not divisible by 2

Exception bit

MA

Volume Chapter 1A

Section

02 Annen

Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-23a Date: 1/8/68

## Load Multiple Arithmetic per Alternate Key LMAA

i j k h

number of registers loaded + j

eal

$$+ X^k + h$$

eak + alternate key

$$A^{i+1} \leftarrow M^{ea+2}$$

$A^{i+j-1} + M^{ea+2j-2}$

If j is zero, 32 registers will be loaded.

Exceptions

missing address ea not divisible by 2

Exception bit

MA

Volume Chapter

1A

Section

: 02 : Appendix IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-23b Date: 1/8/68

## Store Multiple Arithmetic

STMA

| <br> |       |      | <del></del> |  |

|------|-------|------|-------------|--|

|      |       | ١. ا |             |  |

| 1    | l 3 i | K    | l h         |  |

| <br> |       |      |             |  |

number of registers stored + j

eal

$$+ X^{k} + h$$

eak + normal key

$$M^{\text{ea}+2} + A^{i+1}$$

$M^{ea+2j-2} \leftarrow A^{i+j-1}$

If j is zero, 32 registers will be stored.

| Exceptions |

|------------|

|------------|

Exception bit

missing address protected address ea not divisible by 2

MA

PA

Volume

Chapter

: 1A : 02

Section

: Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-23c Date: 1/8/68

## Store Multiple Arithmetic per Alternate Key STMAA

k h

number of registers stored + j

eal

$$+ X^k + h$$

eak + alternate key

$$M^{ea} + A^{i}$$

$$M^{ea+2} + A^{i+1}$$

$$M^{ea+2j-2} + A^{i+j-1}$$

If j is zero, 32 registers will be stored.

| Exce | eptions |

|------|---------|

|------|---------|

Exception bit

missing address protected address ea not divisible by 2

MA

PA

Volume

1A

Chapter

02

Section : Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 1-24 Date: 4/17/67

# Store Multiple Zeros

STMZ

k h

$$eal + X^k + h$$

eak +normal key

$$M^{ea, ea+1, ..., ea+63} + 0 [1536]$$

Exceptions

Exception bit

missing address protected address ea not divisible by 64

MA PA

BV

# Store Multiple Zeros per Alternate Key STMZA

k

h

eal  $+X^{k} + h$

eak +alternate key

This instruction is identical to STMZ except that the alternate key is used.

Exceptions

Exception bit

missing address protected address ea not divisible by 64

AM

PA BV

Volume Chapter : 1A : 02

Section

: Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 2-1 Date: 4/17/67

## MOVE OPERATIONS

The move operations are for transfering data between registers of two different types. Examples are moves from a special register to an index register or from an index register to an arithmetic register. Most of the instructions involve movement of entire registers or register pairs. However there is a class of move instructions which move single bits to or from the condition register.

Movement of information to or from special registers involve certain interlock considerations which are treated in the section, "Interlocking".

Volume Chapter Section

: 1A : 02

: Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 2-2

Date: 4/17/67

| Move | Index | to | Arithm | etic |

|------|-------|----|--------|------|

|      |       |    |        |      |

MXA

$A^{i} \leftarrow X^{j,k}$

Exceptions: none

Move Arithmetic to Index

MAX

$x^{i,j} \in A^k$

If i = j,  $X^i$  will be set to  $A_{24}^k$ , ..., 47.

Exceptions: none

Volume

: 1A

: 02

Chapter Section

: Appendix

# IBM REGISTERED CONFIDENTIAL ACS-I Development Workbook

Page: 2-3 Date: 4/17/67

## Move Constant to Left Half Arithmetic

MKL

h

$$A_{0,1,2,\dots,23}^{i}$$

+h  $A_{24,25,26,\dots,47}^{i}$  +0 [24]

Exceptions: none

## Move Constant to Right Half Arithmetic

MKR

Note that bits  $A_{0,1,2,\cdots,23}^{i}$  are unchanged.

Exceptions: none

Volume

: 1A

Chapter

: 02

Section : Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 2-4 Date: 1/8/68

| <u>Move</u> | <u>Lo</u> | cation | to | Index |

|-------------|-----------|--------|----|-------|

|             |           |        |    |       |

MLX

| <br> |    |

|------|----|

| i    | jk |

$$X^{i}$$

+ia + jk

The value of ia is the 24-bit storage location of the MLX instruction. The 10-bit literal jk-field is extended to a 24-bit quantity before the addition by appending 14 high-order bits equal in value to the high order bit of the jk-field. The addition is performed modulo 224.

Exceptions: none

| Move | Index | to | Spec | cial |

|------|-------|----|------|------|

|      |       |    |      |      |

MXS

s<sup>i</sup> +x<sup>j</sup>

Exceptions

Exception bit

i ≥3 and in problem mode

PV

Move Special to Index

MSX

$x^{i} + s^{j}$

Exceptions

Exception bit

$j \ge 3$  and in problem mode

PV

Volume

: 1A

Chapter

: 02

Section

: Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 2-5 Date: 1/8/68

Move Special to Index and Zero

MSXZ

i j

$$x^{i} + s^{j}$$

$$s^{j} + 0 [24]$$

Exceptions

Exception bit

$j \ge 3$  and in problem mode

PV

Move Index to Special by Oring

MXSO

i j

$$s^i + s^i \checkmark x^j$$

Exceptions

Exception bit

$i \ge 3$  and in problem mode

PV

Volume

Chapter

: 1A : 02

Section

: Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

**Page: 2-6** Date: 1/8/68

|  | Move | Index | Bit | to | Condition | Bit |

|--|------|-------|-----|----|-----------|-----|

|--|------|-------|-----|----|-----------|-----|

MXC

$n + x^k$

$c_i + X_n^j$

If n exceeds 23,  $c_i$  is set to 0.

Exception

Exception bit

$c_{24}$  set to 0 or  $c_{25}$  set to 1

CC

Move Condition Bit to Index Bit

MCX

k

$n + x^k$

$X_n^i + c_i$

If n exceeds 23, no bit is set.

Exceptions: none

Move Arithmetic Bit to Condition Bit

MAC

i k

$n + A^k$

$c_i + A_n^j$

If n exceeds 47,  $c_i$  is set to 0.

Exception

Exception bit

$\mathbf{c}_{24}$  set to 0 or  $\mathbf{c}_{25}$  set to 1

CC

Volume

: 1A

Chapter

: 02

Section

: Appendix

## IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 3-1 Date: 1/8/68

## FLOATING POINT ARITHMETIC

The purpose of the floating point instruction set is to perform calculations using data with a wide range of magnitude and yielding results scaled to preserve precision.

Floating point numbers consist of an exponent E and a fraction F. The quantity expressed by this number is the product of the fraction and the number 2 raised to the power of the exponent, that is:

value =

$$\pm F \times 2^{E}$$

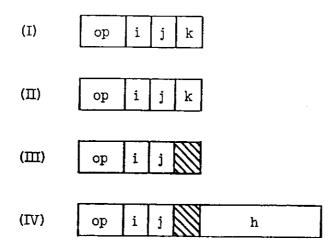

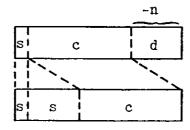

## Instruction Format

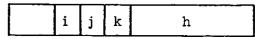

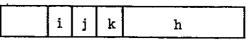

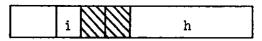

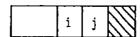

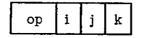

Most floating point instructions have the following format:

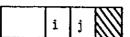

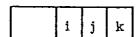

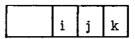

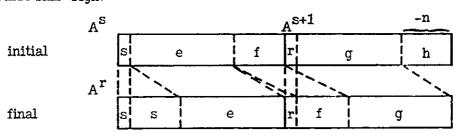

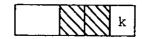

where j and k designate the arithmetic registers containing the source operands and i specifies the result register(s). The remaining floating point operations ignore the k field of the instruction.

The arithmetic registers containing the source operands are not changed as a result of floating point instructions unless they are also specified by the i field to be result registers.

#### Number Representation

Floating point numbers may be in 48 bit single precision form or in 96 bit double precision form. Single precision numbers may occupy any of the arithmetic registers. Double precision numbers may occupy any even-odd pair of arithmetic registers. Arithmetic register  $A^0$  is specified to be a source of 0's. When  $A^0$  is specified as a source operand, 48 or 96 0's will be provided depending on whether a single or double precision operand was called for by the instruction. If  $A^0$  is specified as the result register, the result will be lost, and the only effect of the operation will be a possible change in the exception register.

Whenever a double precision number is specified by an instruction, the value of the i-, j-, or k-field (as appropriate) is assumed to be even. If it is not, the low order bit of the field is forced to 0, exception bit RS is set, and the operation proceeds. Thus fifteen non-zero double precision quantities are specifiable; namely, the data in register pairs specified by 2,4,6,...,30. Note that register A<sup>1</sup> is not the low order half of any double precision quantity.

Volume Chapter : 1A

Section

: 02

: Appendix

#### IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 3-2 Date: 4/17/67

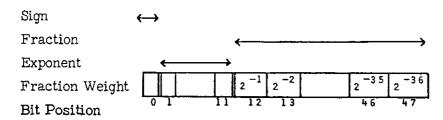

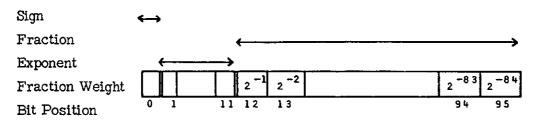

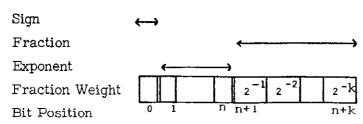

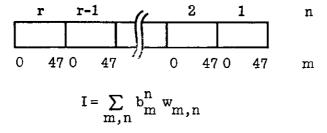

The representation of a floating point number consists of a one bit sign field, an 11 bit exponent field, and a 36 bit or 84 bit fraction field. The sign field occupies positions 0 of the floating point number. A 0 signifies a positive fraction and a 1 a negative fraction. The exponent field occupies positions 1 through 11. The exponent field contains the sum of the exponent, E, and the number 1024, the bias value. The fraction field occupies positions 12 through 47 for a single precision number, and positions 12 through 95 for a double precision number.

Pictorially, with arithmetic bit weights given for the fraction, the formats are:

#### 48 bit floating point number

#### 96 bit floating point number

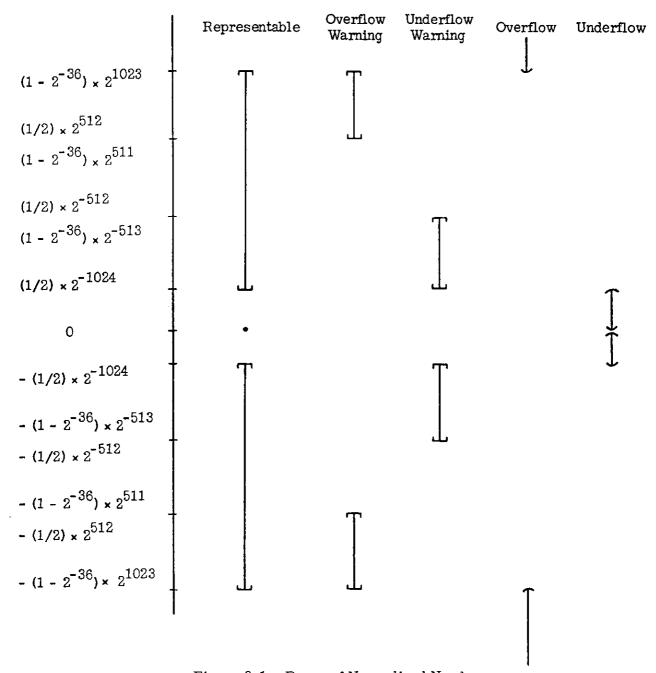

#### Number Range

The range of exponents which can be represented is +1023 through -1024. Whenever a floating point operation results in an exponent which cannot be represented in this range, an exception condition exists. If the exponent exceeds +1023, the condition is called overflow. If the exponent is less than -1024, the condition is called underflow. An appropriate exception bit is set to 1 on occurrence of these exceptional conditions.

Figure 3.1 illustrates the range of normalized results possible from a single precision floating point operation. The range of result magnitude is approximately 2.8  $\times$  10<sup>-309</sup> to 9.0  $\times$  10<sup>307</sup>.

Volume

: 1A

Chapter

: 02

Section

: Appendix

## IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 3-3

Date: 4/17/67

Numbers in the exponent overflow range have the properties of undefined numbers and will be symbolized by u. Furthermore, results in this overflow range are changed to a specific bit configuration: bit zero is set to 1 and the remaining bits are set to 0.

Numbers in the exponent underflow range may be considered to have the properties of the number zero, and are symbolized by 0. Hence, results in the exponent underflow range are changed to the bit configuration which is all 0's.

Since the bit configuration of a leading 1 followed by all 0's represents the u range, special definition of arithmetic using this configuration as an operand is necessary. Figure 3. 2 summarizes the results for initial operands as specified. N represents a non-zero value in the valid number range. N\* represents a result which is normally in the N range but may be in the u or 0 ranges due to exponent overflow or underflow. Results when using these operands in the compare and sign change operations are given in the sections of this manual dealing with those instructions.

In order to inform the programmer when results approach to the limits of representability, there are overflow and underflow warning bits. These bits are set when a machine with a ten bit exponent would overflow or underflow. The resulting operand is not affected by the setting of these exception bits.

#### Normalization

A quantity can be represented with the greatest precision by a floating point number, with a given fraction length, when that number is normalized. A floating point number is normalized when it is zero or when  $1/2 \le |F| < 1$ . Thus, a non-zero floating point number is normalized if bit 12 (the high order fraction bit) is a 1. The process or normalization consists of shifting the fraction left until the high order fraction bit is a 1, and reducing the exponent by the number of bits shifted.

Instructions are provided which allow floating point arithmetic to be performed with either normalized or unnormalized results. The normalized addition and subtraction instructions yield a normalized result regardless of whether or not the input operands were normalized. The normalized multiplication instructions only guarantee a normalized result if both input operands were normalized. Division may not be done with an unnormalized divisor and does not guarantee a normalized result if the dividend is not normalized.

Volume Chapter : 1A

: 02

Section : Appendix IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 3-4 Date: 4/17/67

Figure 3.1. Range of Normalized Numbers

Volume

: 1A

Chapter Section

: 02 : Appendix

# IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 3-5 Date: 4/17/67

#### Addition Table

|        | Addend |    |   |  |

|--------|--------|----|---|--|

| Augend | 0      | N  | u |  |

| 0      | 0      | N  | u |  |

| И      | N      | N* | u |  |

| u      | u      | u  | u |  |

# Multiplication Table

|            | Multiplicand |    |   |  |

|------------|--------------|----|---|--|

| Multiplier | 0            | N  | u |  |

| 0          | 0            | 0  | u |  |

| N          | 0            | И* | u |  |

| u          | u            | u  | u |  |

Division Table

|         | Dividend |    |   |  |  |

|---------|----------|----|---|--|--|

| Divisor | 0        | N  | u |  |  |

| 0       | u        | u  | u |  |  |

| И       | 0        | N* | u |  |  |

| u       | u        | u  | u |  |  |

Figure 3. 2. Result Ranges

Volume Chapter : 1A

Section

: 02

Appendix

## IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 3-6 Date: 4/17/67

## Truncation and Rounding

During the execution of floating point arithmetic operations, low order bits may be truncated in intermediate calculations or when placing the result in the result register. In single precision arithmetic the intermediate result fraction is truncated with the high order 37 bits retained. The low order bit of the retained information is called the guard bit. Normalization, if specified by the instruction, takes place by shifting the intermediate fraction including the guard bit. Following normalization the fraction is truncated to 36 bits and placed in the result register. Double precision normalized arithmetic is similar except the intermediate fraction is truncated with 85 bits retained, and the final result is truncated to 84 bits.

Normalized floating point arithmetic instructions are also provided which specify the result fraction to be statistically rounded. If any of the bits truncated, during either of the truncation processes described above, were a 1, the low order bit of the fraction field is forced to a 1.

Rounding does not take place if a zero fraction, exponent overflow, or exponent underflow exception occurred.

## Low Significance and Zero Fraction

Addition and subtraction may cause a loss of significant bits in cases where the operands are of nearly the same magnitude and differ in sign or when the operands have large numbers of leading 0's, so that the result, before normalization, has a large number of leading 0's. A warning is given when this occurs by setting a "low significance" exception bit to 1. The bit is set to 1 for both single and double precision operations when the leading 1 bit of the result fraction, prior to normalization, is in one of the eight least significant bit positions or is in the guard bit. The low significance exception bit is not set to 1 when the result fraction is all 0's. For this occurrence, a "zero fraction" exception bit is set to 1.

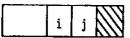

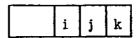

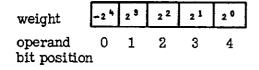

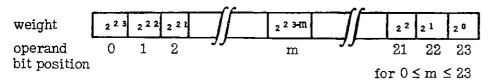

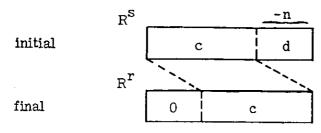

# Short Word Floating Point Format

Special provision is made for allowing floating point numbers to be packed into less than 48 bits. In the short floating point format, the sign bit occupies the leading bit position, the exponent field the next n positions (where n is between one and eleven), and the fraction field the remaining positions. The following diagram illustrates this format:

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 3-7 Date: 4/17/67

Volume : 1A Chapter : 02 Section : Appendix

Quantities in this short format are not acceptable operands for arithmetic operations and must be converted to the standard 48 bit format before use. Two special instructions CVF and CVS are provided for converting from short word to full word floating point and vice versa. These instructions which contract and expand the exponent will be described further in the instruction section.

In the short format the exponent, sign, and fraction fields have the same interpretation as in the long format except that the exponent is stored with a bias of  $2^{n-1}$  in the short format (in the regular format, the bias is  $2^{10}$ ).

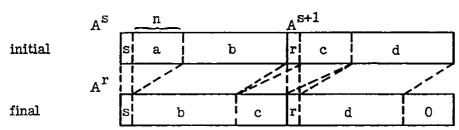

#### Operation Summary

The following table summarizes the floating point arithmetic instructions:

|                                                      | Add            | Subtract       | Multiply         | Divide           |

|------------------------------------------------------|----------------|----------------|------------------|------------------|

| Normalized, Truncated Single Double Mixed            | AN<br>ADN<br>- | SN<br>SDN<br>- | MN<br>MDN<br>MMN | DN<br>DDN<br>DMN |

| Normalized, Rounded<br>Single<br>Double<br>Mixed     | AR<br>ADR<br>- | SR<br>SDR      | MR<br>MDR<br>-   | DR<br>DDR<br>DMR |

| Unnormalized, Truncated<br>Single<br>Double<br>Mixed | AU<br>ADU<br>- | SU<br>SDU<br>- | MU<br>MDU<br>MMU | -<br>-<br>-      |

Volume Chapter : 1A : 02

Section

: Appendix

#### IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 3-8 Date: 4/17/67

# Addition and Subtraction Instructions

All the addition and subtraction operations are performed as follows:

The notation 37/85 indicates 37 in the case where the result is to be in single precision and 85 in the case where the result is to be in double precision.

- 1. If either operand is a u, the result is set to u and the remaining steps of the operations are omitted.

- 2. If either operand is 48/96 0's, step 3 is omitted. If both of the operands are 48/96 0's, the result is set to 48/96 0's and the remaining steps are omitted.

- 3. The exponents of the operands in  $A^j$  and  $A^k$  are compared and the fraction of the operand with the smaller exponent is shifted right a number of positions equal to the difference in exponents. O's are inserted in the high order vacated bits.

- 4. If the instruction specifies subtraction, the sign of the second operand is changed.

- 5. A signed fraction addition then takes place with the high order bit of the shifted fraction aligned with the high order bit of the unshifted fraction. Conceptually, addition takes place before any truncation and the intermediate result is then truncated to 37/85 bits. In fact, truncation takes place first, with sufficient information retained from the truncated bits to make the above property hold.

- 6. The larger of the two operand exponents is taken as the exponent of the intermediate result.

- 7. If the fraction addition caused a fraction overflow, the intermediate fraction is shifted right one position and a 1 is inserted in the high order position. One is then added to the intermediate exponent. If this causes the exponent to exceed 1023 an exponent overflow has occurred. The result is then set to u, the AO (add overflow) exception bit is set to 1, and the remaining steps are omitted.

- 8. If normalization is specified and if the 37/85 bit intermediate result fraction was all 0's, the result is set to zero (i. e. 48/96 0's), the ZF (zero fraction) exception bit is set to 1, and the remaining steps are omitted.

- 9. If normalization is not specified and the 36/84 bit intermediate result fraction was all 0's, the ZF exception bit is set to 1 and step 10 is omitted.

- 10. If the high order 28/76 bits of the fraction are all 0's the LS (low significance) exception bit is set to 1.

Volume Chapter

1A

02

Section Appendix IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 3-9

Date: 4/17/67

11. If the instruction specified normalization, the intermediate fraction is now normalized. The intermediate fraction is shifted left until its high order bit is a 1. O's are inserted into the low order vacated bits. The intermediate exponent is decreased by the amount of the shift. If this causes the exponent to be less than -1024, an exponent underflow has occurred. The AU (add underflow) exception bit is set to 1, the result is set to 48/96 0's and the remaining steps are omitted.

- If the resulting exponent is greater than 511, the OW (overflow warning) exception bit 12. is set to 1. If the resulting exponent is less than -512, the UW (underflow warning) exception bit is set to 1.

- This intermediate result fraction is truncated to 36/84 bits. 13.

- 14. If rounding was specified by the operation, the low order bit of the fraction is forced to a 1 if any of the truncated bits, including the bit shifted out in step 7, were a 1.

Volume Chapter 1A

Chapter : 02 Section : Appendix IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 3-10 Date: 1/8/68

## Add Normalized

AN

i j k

The contents of register  $A^i$  are replaced by the normalized sum of the single precision floating point numbers in  $A^j$  and  $A^k$ .

| Exceptions                     | Exception bit |

|--------------------------------|---------------|

| result exponent > +1023        | AO            |

| result exponent < -1024        | AU            |

| +511 < result exponent ≤ +1023 | OW            |

| -512 > result exponent ≥ -1024 | UW            |

| low significance               | LS            |

| zero fraction                  | ZF            |

# Add Double Normalized

ADN

i j k

The contents of register pair  $A^{i,i+1}$  are replaced by the normalized sum of the double precision floating point numbers in  $A^{i,i+1}$  and  $A^{i,k+1}$ .

| Exceptions                     | Exception bit |

|--------------------------------|---------------|

| result exponent > +1023        | AO            |

| result exponent < -1024        | AU            |

| ÷511 < result exponent ≤ +1023 | OW            |

| -512 > result exponent ≥ -1024 | wu            |

| low significance               | LS            |

| zero fraction                  | ${f ZF}$      |

| i, j, or k odd                 | RS            |

Volume Chapter 1A

Section

02

Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 3-11 Date: 1/8/68

## Add Rounded

AR

| <br> |   |   |

|------|---|---|

| 1    | j | k |

The contents of register  $A^i$  are replaced by the normalized and statistically rounded sum of the single precision floating point numbers in  $A^i$  and  $A^k$ .

| Exceptions                     | Exception bit |

|--------------------------------|---------------|

| result exponent > +1023        | AO            |

| result exponent < -1024        | AU            |

| +511 < result exponent ≤ +1023 | WO            |

| -512 > result exponent ≥ -1024 | <b>w</b> u    |

| low significance               | LS            |

| zero fraction                  | $z_{F}$       |

# Add Double Rounded

ADR

The contents of register pair  $A^{i,i+1}$  are replaced by the normalized and statistically rounded sum of the double precision floating point numbers in  $A^{j,j+1}$  and  $A^{k,k+1}$ .

| Exceptions                               | Exception bit |

|------------------------------------------|---------------|

| result exponent > +1023                  | AO            |

| result exponent < -1024                  | UA            |

| +511 < result exponent ≤ +1023           | OW            |

| -512 > result exponent <u>&gt;</u> -1024 | UW            |

| low significance                         | LS            |

| zero fraction                            | $z_{F}$       |

| i, j, or k odd                           | RS            |

|                                          |               |

Volume

1A

Chapter Section 02

: Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook Page: 3-12

Page: 3-12 Date: 1/8/68

# Add Unnormalized

AU

The contents of register  $A^{\hat{i}}$  are replaced by the unnormalized sum of the single precision floating point numbers in  $A^{\hat{i}}$  and  $A^{\hat{k}}$ .

| Exceptions                    | Exception bit |  |

|-------------------------------|---------------|--|

| result exponent > +1023       | AO            |  |

| +511 < result exponent ≤+1023 | OW            |  |

| low significance              | LS            |  |

| zero fraction                 | ZF            |  |

## Add Double Unnormalized

ADU

The contents of register pair  $A^{i,i+1}$  are replaced by the unnormalized sum of the double precision floating point numbers in  $A^{i,i+1}$  and  $A^{k,k+1}$ .

| Exceptions                    | Exception bit |  |

|-------------------------------|---------------|--|

| result exponent > +1023       | AO            |  |

| +511 < result exponent ≤+1023 | wo            |  |

| low significance              | LS            |  |

| zero fraction                 | $z_{ m F}$    |  |

| i, j, or k odd                | RS            |  |

Volume

: 1A

Chapter Section : 02

Section : Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook Page: 3-13 Date: 1/8/68

#### Subtract Normalized

SN

| , |   | 1- |

|---|---|----|

| 1 | j | K  |

The contents of register  $A^{\hat{i}}$  are replaced by the normalized result of the subtraction of the single precision floating point number in  $A^{\hat{k}}$  from the single precision floating point number in  $A^{\hat{j}}$ .

| Exceptions                     | Exception bit          |

|--------------------------------|------------------------|

| result exponent > +1023        | AO                     |

| result exponent < -1024        | AU                     |

| +511 < result exponent ≤+1023  | OW                     |

| -512 > result exponent ≥ -1024 | WU                     |

| low significance               | LS                     |

| zero fraction                  | $\mathbf{Z}\mathbf{F}$ |

#### Subtract Double Normalized

SDN

The contents of register pair  $A^{i,i+1}$  are replaced by the normalized result of the subtraction of the double precision floating point number in  $A^{k,k+1}$  from the double precision floating point number in  $A^{i,i+1}$ .

| Exceptions                     | Exception bit |

|--------------------------------|---------------|

| result exponent > +1023        | AO            |

| result exponent < -1024        | AU            |

| +511 < result exponent ≤ +1023 | WO            |

| -512 > result exponent ≥ -1024 | wu            |

| low significance               | LS            |

| zero fraction                  | $z_{	t F}$    |

| i, j, or k odd                 | RS            |

Volume

: 1A

Chapter

: 02

Section : Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 3-14 Date: 1/8/68

#### Subtract Rounded

SR

i j k

The contents of register  $A^i$  are replaced by normalized and statistically rounded result of the subtraction of the single precision floating point number in  $A^k$  from single precision floating point number in  $A^j$ .

| Exceptions                     | Exception bit |

|--------------------------------|---------------|

| result exponent > +1023        | AO            |

| result exponent < -1024        | AU            |

| +511 < result exponent ≤+1023  | OW            |

| -512 > result exponent ≥ -1024 | UW            |

| low significance               | LS            |

| zero fraction                  | $z_{F}$       |

#### Subtract Double Rounded

SDR

The contents of register pair  $A^{i,i+1}$  are replaced by the normalized and statistically rounded result of the subtraction of the double precision floating point number in  $A^{k,k+1}$  from the double precision floating point number in  $A^{j,j+1}$ .

| Exceptions                     | Exception bit |

|--------------------------------|---------------|

| result exponent > +1023        | OA            |

| result exponent < -1024        | AU            |

| +511 < result exponent ≤ +1023 | OW            |

| -512 > result exponent ≥ -1024 | UW            |

| low significance               | LS            |

| zero fraction                  | ZF            |

| i, j, or k odd                 | RS            |

Volume

1A

Chapter Section : 02

Appendix

#### IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 3-15 Date: 1/8/68

## Subtract Unnormalized

SU

i j k

The contents of register  $A^i$  are replaced by the unnormalized result of the subtraction of the single precision floating point number in  $A^k$  from the single precision floating point number in  $A^j$ .

| Exceptions                    | Exception bit |  |

|-------------------------------|---------------|--|

| result exponent > +1023       | OA            |  |

| +511 < result exponent ≤+1023 | OW            |  |

| low significance              | LS .          |  |

| zero fraction                 | ZF            |  |

# Subtract Double Unnormalized

SDU

The contents of register pair  $A^i$ , i+1 are replaced by the unnormalized result of the subtraction of the double precision floating point number in  $A^k$ , k+1 from the double precision floating point number in  $A^j$ , j+1.

| Exceptions                    | Exception bit    |

|-------------------------------|------------------|

| result exponent > +1023       | AO               |

| +511 < result exponent ≤+1023 | OW               |

| low significance              | LS               |

| zero fraction                 | $z_{\mathrm{F}}$ |

| i, j, or k odd                | RS               |

Volume

: 1A

Chapter

: 02

Section

: Appendix

# IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 3-16 Date: 4/17/67

#### Multiplication Instruction

The multiplication operations are performed as follows:

- 1. If either operand is u, the result is set to u and the remaining steps of this operation are omitted.

- If either operand is 48/96 0's, the result is set to zero and the remaining steps are omitted.

- 3. If either operand is unnormalized and the instruction calls for normalization, the UO is set to 1.

- 4. The exponents of the operands are added to form an intermediate exponent.

- 5. The 36/84-bit fraction of the operand in A<sup>j</sup> and the 36/84-bit fraction of the operand in A<sup>k</sup> are multiplied to form a 72/168-bit product which is then truncated with the high order 37/85 bits being retained.

- 6. If normalization was called for, the high order bit of the intermediate fraction is compared to 0. If it is a 0, a left shift of one position takes place and the intermediate exponent is decreased by one. This is sufficient to normalize the result if the operands were normalized.

- 7. If the intermediate exponent is greater than 1023, the MO (multiply overflow) exception bit is set to 1 and the result is set to u. The remaining steps are omitted.

- 8. If the intermediate exponent is less than -1024, the MU (multiply underflow) exception bit is set to 1 and the result is set to 48/96 0's. The remaining steps are omitted.

- 9. If the exponent is greater than 511, the OW bit is set to 1. If it is less than -512, the UW bit is set to 1.

- 10. The intermediate fraction is truncated to 36/84 bits.

- 11. If rounding is called for and if any of the truncated bits were a 1, the low order bit of the fraction is set to 1.

Volume

1A

Chapter Section 02

: Appendix

IBM REGISTERED CONFIDENTIAL

ACS-I Development Workbook

Page: 3-17 Date: 1/8/68

## Multiply Normalized

MN

|     |   |     | $\overline{}$ |

|-----|---|-----|---------------|

|     | 1 | 4   | ŀ             |

| l i |   | ן ט | 1.            |

The contents of register  $A^i$  are replaced by the normalized product of the single precision floating point numbers in  $A^j$  and  $A^k$ .

| Exceptions                     | Exception bit |

|--------------------------------|---------------|

| result exponent > +1023        | MO            |

| result exponent < -1024        | MU            |

| +511 < result exponent ≤ +1023 | ow            |

| -512 > result exponent ≥ -1024 | uw            |

| unnormalized operand           | υO            |

# Multiply Double Normalized

MDN